作為個人電腦、伺服器、儲存設備基礎I/O介面的PCIe,也可以稱作「I/O介面的I/O介面」,幾乎所有周邊裝置或其他I/O介面,都是直接或間接透過PCIe的介接,來與運算核心連結。這也意味著,PCIe介面規格的更新,將牽一髮而動全身,在IT架構的發展上,勢必影響與帶動所有周邊裝置與其他I/O介面的發展。

自2003年問世以來,迄今PCIe的發展正好經歷了20年時間,然而自2010年代初期以來的10年間,整個PCIe規格的應用長期停滯在3.0,直到過去半年多以來,PCIe介面規格與應用才終於出現重要的新進展。

PCIe 4.0終於度過漫長、艱苦的推廣階段,開始進入主流應用。而新一代PCIe 5.0的應用則進入推廣的起步階段,第一波支援PCIe 5.0的產品已陸續問世,另一方面,負責規格制定的PCI-SIG組織(PCI Special Interest Group),也於2022年初,完成下一世代PCIe 6.0規格的制定。而這一系列新發展,將在接下來的幾年中,成為推動高速裝置與I/O介面發展的源頭。

PCIe規格的更新週期

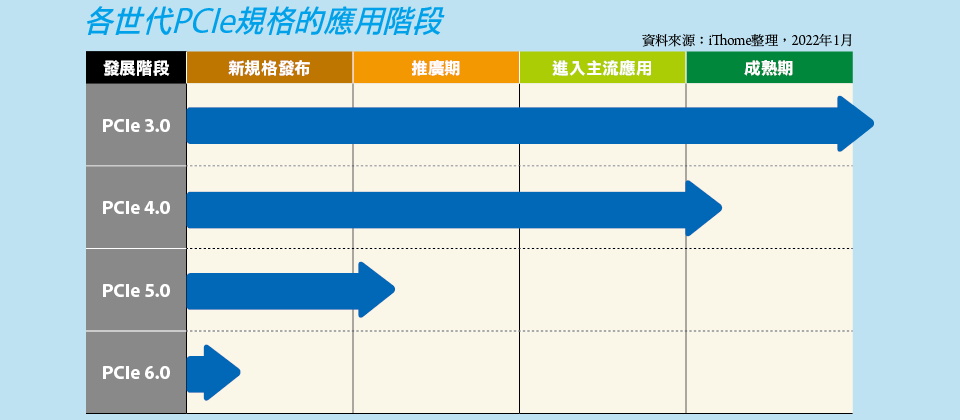

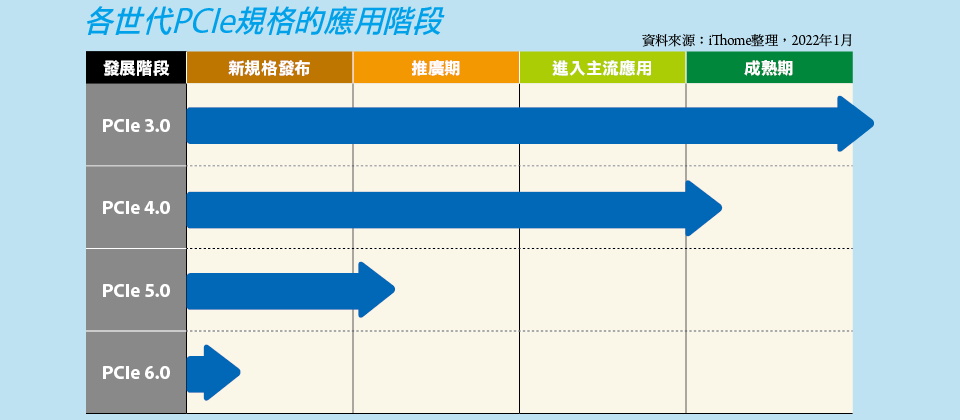

依照過去PCIe介面的發展與應用歷程,我們可以把PCIe介面規格的發展與普及過程,分為4個階段:「新規格發布」、「推廣期」、「進入主流應用」,以及「成熟期」。

(1)新規格發布:每一代PCIe規格應用的起點,是始自PCI-SIG組織完成新一代PCIe規格的制定與發布。在新規格發布前、後,相關的元件廠商,也將陸續推出搭配新PCIe規格的控制元件產品。

(2)推廣期:大約在新PCIe規格制定完成後12至18個月,開始會有廠商推出支援新PCIe規格的周邊裝置產品,如SSD、高速網路卡或GPU加速卡,推廣與帶動新一代PCIe規格的應用。

(3)進入主流應用:在周邊裝置開始支援新PCIe規格過後12至18個月,電腦與伺服器的處理器與晶片組也開始支援新PCIe規格,讓新PCIe規格進入電腦與伺服器,從而開始提供主流核心平臺的應用。

(4)成熟期:當伺服器開始支援新PCIe規格過後12至18個月,儲存陣列等外部儲存設備也開始導入新PCIe規格。一般來說,儲存設備的核心架構更新,要比伺服器慢一個世代,所以當儲存設備也開始採用新PCIe規格的時候,也代表著這一世代PCIe規格進入成熟期,開始全面普及。

總體來說,PCIe規格大約每隔3至4年便會更新一代,而每一代PCIe規格大約也需要3至4年時間,才會度過從規格發布到成熟期的4階段歷程,逐步滲透到IT基礎設施的各個環節,而當一個世代的PCIe規格全面普及時,下一世代的PCIe規格也會跟著問世,開始下一輪的PCIe規格更新循環。

在典型的PCIe規格更新週期下,市場上通常只會同時存在2個世代的PCIe規格,最多不超過3個世代,當新一代規格發表時,上一代規格正處於主流應用與成熟期階段,而上上一代規格則會淡出市場。

四代同堂的PCIe應用特殊現象

以典型的PCIe規格更新週期來看,2010年問世的PCIe 3.0,應該早就退出市場主流,現在的主流規格理當是PCIe 4.0,而下一代的PCIe 5.0則將開始進入推廣階段。

但由於PCIe 4.0的普及速度較預期慢了許多,導致PCIe的主流規格繼續長期停滯在PCIe 3.0,接下來,隨著PCIe 5.0與6.0規格陸續推出,以致在近半年來,形成PCIe 3.0、4.0、5.0、6.0等4個世代PCIe規格並存的異常情況。

姍姍來遲的PCIe 4.0

當前PCIe「四代同堂」異常狀況的形成,是PCIe 4.0推廣過於緩慢所致,而PCIe 4.0的應用之所以如此姍姍來遲,主要可以歸因於這兩點:

首先,PCI-SIG制定PCIe 4.0規格的時間,就已經延宕了。依照PCIe 1.0到PCIe 3.0的規格更新節奏來看,相對於2010年發布的PCIe 3.0,PCIe 4.0規格應該要在2014或2015年發布,但實際上,PCI-SIG直到2017年中才發布PCIe 4.0,較預期晚2、3年,這連帶也推遲了應用的時間。

其次,是作為處理器平臺龍頭廠商的Intel,未能及時支援PCIe 4.0。當PCIe 4.0於2017年底發布後,在2019年前後進入推廣期,除了獲得一些網路卡與SSD產品的支援之外,在主機與伺服器平臺方面,也有IBM的Power 9,以及AMD的Zen 2架構處理器平臺支援,而後者的支援,也讓PCIe 4.0進入了x86平臺應用領域。

然而身為處理器平臺領域領導者的Intel,遲遲不願支援PCIe 4.0,導致PCIe 4.0一直無法真正進入主流應用階段。這個僵局直到2020年後才打開,但Intel平臺對PCIe 4.0的支援,仍要等到2021年中才落實,至此,PCIe 4.0也才算是開始進入主流應用階段。

在前述這兩個因素共同作用下,大大延遲了PCIe 4.0普及的速度。依照過去幾代PCIe規格的應用歷程,自新的PCIe規格發布到進入主流應用階段,大約只需2年多。然而在PCIe 4.0上,從規格發表到開始進入主流應用,卻花了將近4年,再加上PCIe 4.0規格發布本身就「遲到」2、3年,導致整個PCIe規格的更新節奏,在4.0這一世代,出現了5、6年以上的遲滯。

PCIe規格演進延遲的影響

PCIe 4.0的「遲到」,造成了兩項重大影響:

首先,導致PCIe 3.0的生命週期大幅延長,進而對儲存與網路傳輸架構的發展形成了障礙。

歷經10年的發展與應用後,PCIe 3.0依舊是當前的主流規格。最初這沒有帶來太大負面影響,在過去的應用環境中,需要耗用大量PCIe資源的裝置並不多,PCIe 3.0已能因應絕大多數伺服器或儲存設備的應用需求,少數需要大量PCIe通道的裝置(如GPU),也能透過匯聚多條通道的PCIe 3.0 x16來滿足。

但問題在於:當SSD也開始使用PCIe通道作為傳輸介面時,便讓主機板的PCIe傳輸通道(lane)資源,頓時陷入緊繃。

隨著NVMe介面在SSD應用的普及,使得伺服器或儲存設備的PCIe傳輸通道耗用大幅增加。為了獲得足夠的傳輸頻寬,一臺NVMe SSD便需占用4條PCIe 3.0通道,因此,1臺標準的2U伺服器若插滿24臺NVMe SSD,便須占用多達96條PCIe 3.0傳輸通道,從而耗掉伺服器主機板大多數的PCIe資源。

此外,新一代的100GbE、200GbE與400GbE等高速網路連線規格,也需要耗用更多的PCIe傳輸通道資源,才能實現更高的傳輸率。

無論如何,隨著電腦、伺服器、儲存設備採用需更多PCIe通道的裝置,也意味著,若單靠PCIe 3.0,勢必將成為制約儲存與網路傳輸架構發展的瓶頸。

面對這個情況,除了持續增加伺服器主機板的PCIe通道數量,根本的解決辦法便是引進PCIe 4.0——因為PCIe 4.0擁有兩倍於PCIe 3.0的單一傳輸通道頻寬,因而能透過較少的傳輸通道,來為周邊裝置提供足夠的傳輸頻寬。

新舊規格並存的局面,可能將長期維持

在NVMe與高速網路應用的帶動下,使得伺服器與儲存設備領域的PCIe架構應用,終於在2021年開始進入4.0時代。

而在PCIe 4.0緩慢的應用普及過程中,新一代的PCIe 5.0與6.0也接踵而來。

歷經PCIe 4.0規格制定的嚴重延宕後,PCI-SIG組織加速制定新規格的腳步,更新節奏縮短到2年。PCIe 4.0規格是2017年6月正式發布,2年後,PCI-SIG組織便在2019年5月正式發布PCIe 5.0規格,接著只隔了1年半多,便又在2022年1月發布PCIe 6.0規格。

而在實際應用方面,剛剛發布的PCIe 6.0自然還尚無具體進展,不過PCIe 5.0已經進入初步的推廣期,自2021年底開始,便開始有廠商推出支援PCIe 5.0的高速網路卡與SSD產品。

因而,這也讓當前的PCIe應用環境,形成了3.0、4.0、5.0、6.0「四代同堂」的奇特現象。

整體而言,PCIe 4.0近期進入主流應用,先後滲透到伺服器與儲存設備,但上一代的PCIe 3.0,多年來累積龐大應用基礎,短期內仍不會退出主流,加上新一代PCIe 5.0與PCIe 6.0崛起,陸續投入應用,因而我們可以預期,當前這種4個PCIe世代並存局面,仍將繼續維持。

PCIe規格的更新時序

從PCI-SIG組織發布歷代PCIe規格的時間,我們可以明顯看出:PCIe 3.0到PCIe 4.0之間,間隔了特別長的時間。自PCIe 1.0到3.0之間,大約是3至4年更新一代,而從4.0到6.0,縮短到每隔2年便更新一代,但PCIe 3.0到4.0之間相隔將近7年。相較於「正常」的更新節奏,PCIe 4.0的問世時間「遲到」了3年以上。

而PCIe 4.0的「遲到」,也導致PCIe規格的應用長期停滯在3.0上。接下來PCI-SIG組織加速制定新規格的腳步,接連在2019年中與2022年初推出PCIe 5.0與6.0等2種新規格,但也形成了PCIe 3.0、4.0、5.0、6.0等4世代規格,同時並存的情況。

歷代PCIe規格發表時間

2003年:PCIe 1.0

2007年:PCIe 2.0

2010年:PCIe 3.0

2017年:PCIe 4.0

2019年:PCIe 5.0

2022年:PCIe 6.0

資料來源:iThome整理,2022年1月

4世代PCIe規格應用現況

依照規格普及與產品應用的情況,我們可以將PCIe規格的發展歷程,分成下列4個階段——新規格發布、推廣期、進入主流應用與成熟期。目前,同時並存於市場上的4個世代PCIe規格——PCIe 3.0、4.0、PCIe 5.0與PCIe 6.0,各自處於不同的發展階段。

問世於2010年,應用已超過10年的PCIe 3.0,雖然是早已進入成熟期的上一世代技術,但目前仍然是主流規格之一,仍將繼續留存在市場上一段長時間。

在PCIe 4.0方面,自2017年中發布規格後,雖在2019年便滲透到伺服器應用,但直到Intel平臺於2021年大舉支援PCIe 4.0,才算開始進入主流應用;緊接著,從2021年中,HPE、Pure Storage等儲存廠商開始將PCIe 4.0,用於儲存陣列產品,象徵這項規格終於進入成熟階段初期。

再來是2019年中發布的PCIe 5.0,則於2021年底到2022年初,出現了第1批支援的周邊裝置與電腦平臺產品,代表進入了發展的推廣期。

最後是PCIe 6.0,PCI-SIG自2019年中發布了最初的規格草案,經過2年半的發展,於2022年1月正式發布了規格,讓這個最新世代的PCIe規格進入了應用的起點,預期2年之後,便會有第1批支援的周邊產品問世。

PCIe的進化

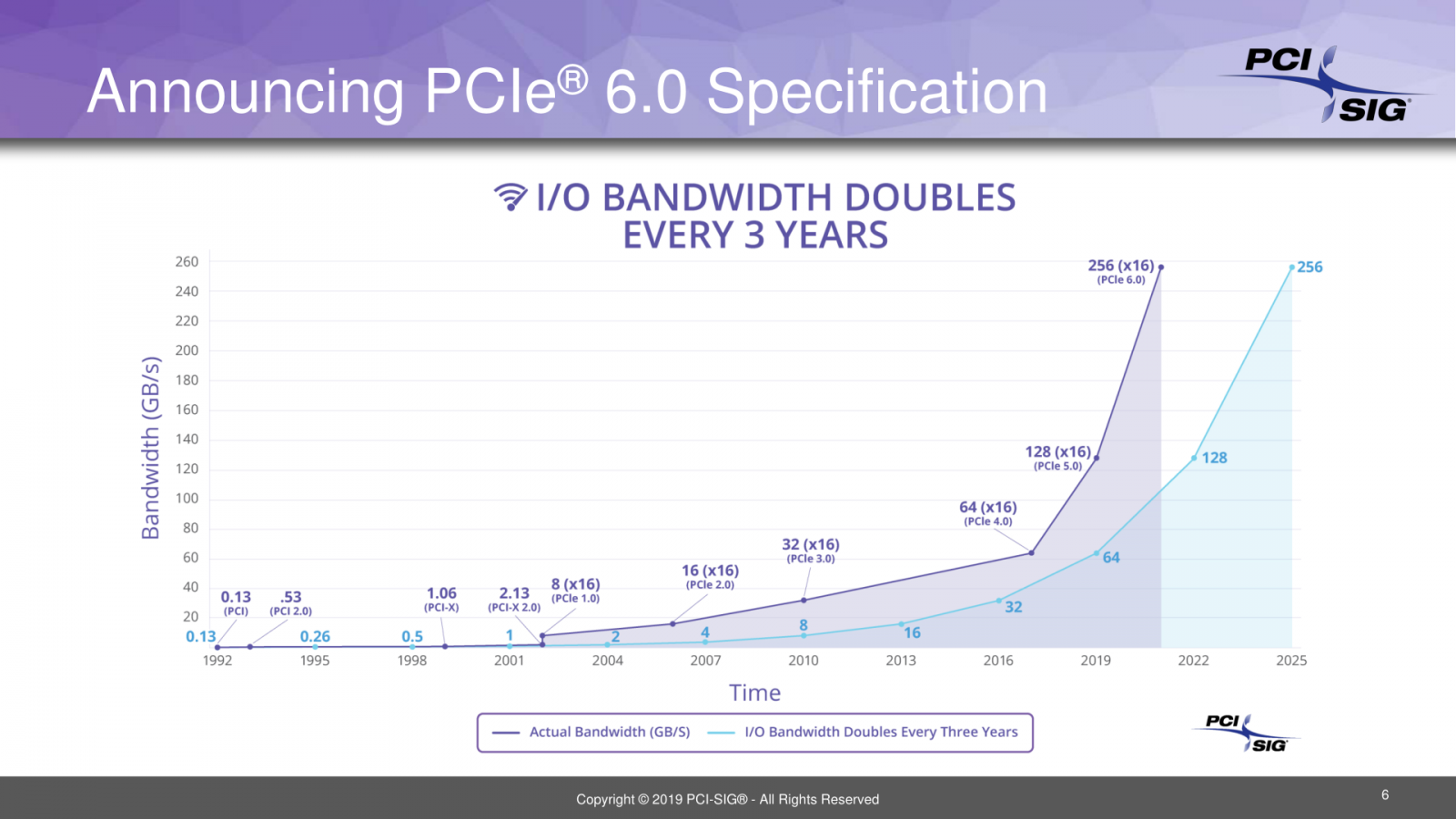

PCI/PCIe帶動的傳輸頻寬增長

從1992年誕生的PCI技術起算,歷經過渡的PCI-X、2003年問世的PCIe,以至甫於2022年初正式發布的PCIe 6.0,電腦I/O技術在30年內提升了200倍的傳輸頻寬,平均每3年提升了2倍。圖片來源/PCI-SIG

就應用方式而言,PCIe是一種高速串列匯流排,作為電腦內部各元件與CPU之間傳輸資料的主要幹道。

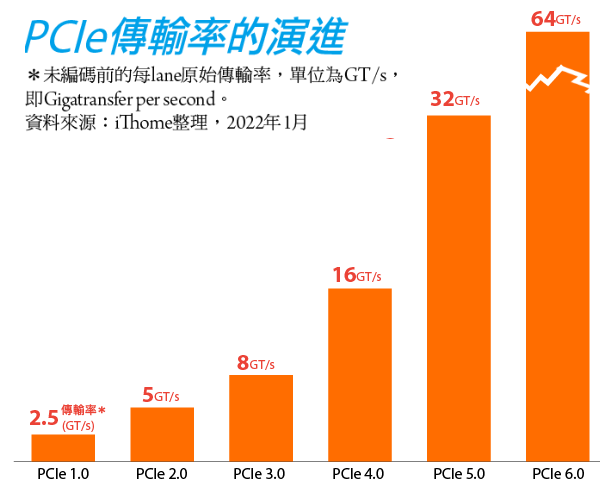

自2003年問世到2022年初為止,PCIe一共推出6個世代,每個新世代的傳輸速率,都比前個世代提高一倍,但2.0到3.0是例外,只提高60%。

PCIe匯流排的原始傳輸速率,是以GT/s為單位,即Gigatransfer per second。其實際的傳輸速率,會隨著傳輸信號的編碼方式,以及所使用的通道(lane)數量而異。

自PCIe 1.0到5.0,都是採用不歸零(Non-Return-to-Zero,NRZ)編碼技術,其中1.0與2.0是使用8b/10b型式的編碼,也就是10位元編碼輸出中含有8位元有效資料; 3.0、4.0與5.0改用較新的128b/130b編碼,130位元的編碼輸出中含有128位元有效資料,有效頻寬更高。所以PCIe 3.0的原始傳輸率雖然只比2.0提高60%,但憑藉編碼的改進,實際有效頻寬提升近一倍。

至於PCIe 6.0,則採用了4級脈波振幅調變編碼技術(Pulse-amplitude modulation-4,PAM-4),但為了彌補PAM-4較高的錯誤率,另搭配前向錯誤校正(Forward Error Correction,FEC)),雖然當中略為降低了有效頻寬,但仍實現大約2倍於PCIe 5.0頻寬的設計目的(實際上是1.92倍)。

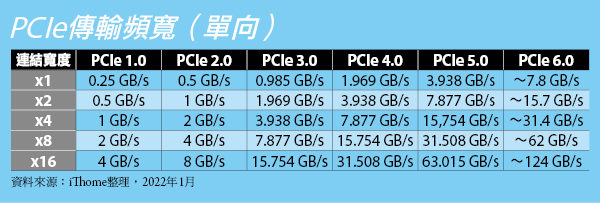

依使用的傳輸通道數量,PCIe有x1、x2、x4、x8、x16等不同的連結傳輸寬度(link width),代表使用1條、2條、4條、8條與16條傳輸通道。

最初的PCIe 1.0,每條傳輸通道可提供2.5 GT/s傳輸率,到了最新的PCIe 6.0則為64 GT/s,在20年內提高了25.6倍的速度。若從PCIe前身的PCI規格起算,1992年誕生的PCI 1.0傳輸率為133 MB/s,相較下,PCIe 6.0的傳輸率足足提升為200倍之多,也就是說30年內提升200倍頻寬,因而PCI-SIG組織宣稱,在PCI/PCIe技術的帶動下,I/O頻寬平均每3年可提升2倍。

Read Rhis 👉 新聞來源

——

吹水:Just Share

t.me/BuzzerShare

——

via NG JCbwre7L

#臺灣 #TWN 🇹🇼

#iThomeOnline

留言

張貼留言